Designing New Memory Systems for Next-Generation Data Centers

by

Howard Mao

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Randy H. Katz, Chair Professor Krste Asanović Professor Ian Holmes

Fall 2020

Designing New Memory Systems for Next-Generation Data Centers

Copyright 2020 by Howard Mao

#### Abstract

#### Designing New Memory Systems for Next-Generation Data Centers

by

Howard Mao

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Randy H. Katz, Chair

In recent years, there has been a trend towards greater use of DRAM in data center applications. In-memory key-value stores are being used to cache or replace disk-based databases, and memory-based big data frameworks are supplanting earlier disk-based frameworks. However, process technology improvements for DRAM have not kept pace and instead have stagnated in terms of cost and density. With next-generation memory technologies like STT-MRAM, PCRAM, and RRAM still far from commercial viability, improving memory utilization is the most potentially fruitful path towards reducing the cost of data center memory in the near term. A typical way to improve utilization of a resource in a data center is to disaggregate said resource, allowing it to be shared across multiple nodes. Disaggregating memory has generally been quite difficult because the latency of a round-trip across a typical data center network is much greater than the latency of a DRAM access. However, recent work on photonic interconnects promises to deliver data center networks with much lower latencies, making the concept of data center remote memory more feasible.

In this work, we present the design of a DRAM caching remote memory system which divides a data center rack into compute-specialized and memory-specialized nodes. Each memory blade contains a fixed-function hardware controller that serves data from its large pool of DRAM to the compute blades through the rack network. Each compute blade contains a small local DRAM that is used as a cache for remote memory. This local DRAM is managed by a hardware controller which automatically refills the cache on misses by sending requests to remote memory. This system provides a global pool of memory that can be dynamically allocated among the compute blades and is transparent to software. We evaluated our system using microbenchmarks and realistic data center applications in cloud FPGA-based RTL simulations. Through these evaluations, we found that our DRAM caching system can serve data at lower latencies than earlier virtual memory-based remote memory systems and, with the aid of prefetching, can achieve performance comparable to local DRAM.

i

# Contents

| Co            | ntents                                                                                                                                                                               |   |               |   | ii                                                                                                      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------|---|---------------------------------------------------------------------------------------------------------|

| Li            | t of Figures                                                                                                                                                                         |   |               |   | iv                                                                                                      |

| $\mathbf{Li}$ | t of Tables                                                                                                                                                                          |   |               |   | vi                                                                                                      |

| 1             | Introduction         1.1       The End of DRAM Cost/Density Scaling                                                                                                                  | • | <br><br><br>• |   | $     \begin{array}{c}       1 \\       1 \\       2 \\       3 \\       5 \\       6     \end{array} $ |

|               | 1.6       Thesis Contributions and Overview                                                                                                                                          |   |               |   | 6                                                                                                       |

| 2             | Background on Remote Memory Systems2.1Early Disaggregated Memory Systems2.2Modern Disaggregated Memory Systems2.3Chapter Summary and Discussion                                      | • | <br>•         | • | <b>8</b><br>8<br>11<br>18                                                                               |

| 3             | Background on DRAM Caching         3.1       Cache Line Size and Location of Metadata         3.2       Optimizing Latency vs. Optimizing Hit Rate         3.3       Chapter Summary |   | <br>•         | • | <b>19</b><br>20<br>24<br>25                                                                             |

| 4             | Hardware Generators4.1The Chisel Hardware Design Language4.2Chisel Libraries4.3Chapter Summary                                                                                       |   | <br>•         | • | 27<br>27<br>31<br>37                                                                                    |

| 5             | Simulation Platform5.1Golden Gate5.2FireSim5.3Chapter Summary                                                                                                                        |   | <br>•         |   | <b>39</b><br>40<br>42<br>47                                                                             |

| ٠ | ٠ | ٠ |  |

|---|---|---|--|

| 1 | 1 | 1 |  |

| т | T | T |  |

| 6        | Memory Blade and Remote Memory Client Implementation | 48 |

|----------|------------------------------------------------------|----|

|          | 6.1 Remote Memory Protocol                           | 48 |

|          | 6.2 Hardware Design                                  | 50 |

|          | 6.3 Benchmarks                                       | 52 |

|          | 6.4 Chapter Summary                                  | 55 |

| <b>7</b> | DRAM Cache Design                                    | 57 |

|          | 7.1 System Overview                                  | 57 |

|          | 7.2 Cache Controller                                 | 58 |

|          | 7.3 Prefetcher                                       | 60 |

|          | 7.4 Microbenchmark                                   | 62 |

|          | 7.5 SAXPY Benchmark                                  | 64 |

|          | 7.6 Chapter Summary                                  | 67 |

| 8        | Evaluation of DRAM Cache System                      | 68 |

|          | 8.1 Memcached                                        | 68 |

|          | 8.2 Graph Algorithms                                 | 71 |

|          | 8.3 Chapter Summary                                  | 77 |

| 9        | Conclusion                                           | 79 |

|          | 9.1 Dissertation Summary and Contributions           | 79 |

|          | 9.2 Future Work                                      | 80 |

| Bi       | oliography                                           | 83 |

# List of Figures

| mark [42]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 DRAM Cost over 11me                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -2       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 1.3 DRAM Size over Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

| 1.4 Comparison of SRAM, DRAM, FLASH, and NVRAM [41]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 1.5 Memory Bandwidth Utilization [17]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

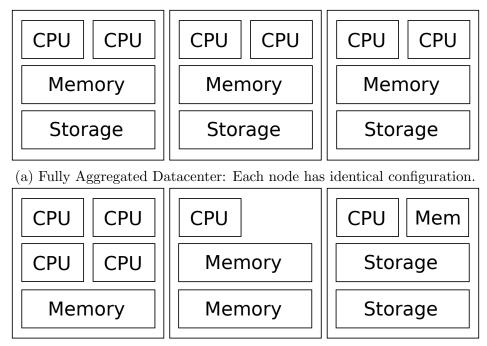

| 1.6 Fully Aggregated vs. Fully Disaggregated Datacenter Organizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5        |

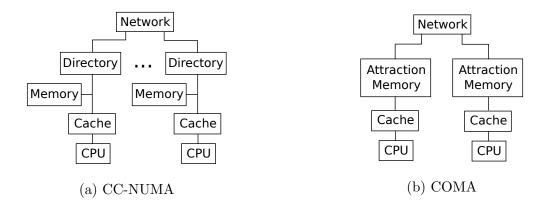

| 2.1 CC-NUMA vs. COMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9        |

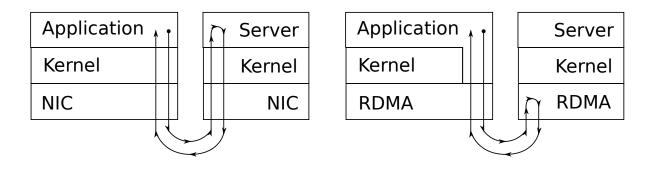

| 2.2 Remote memory access in TCP/IP (left) vs. RDMA (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12       |

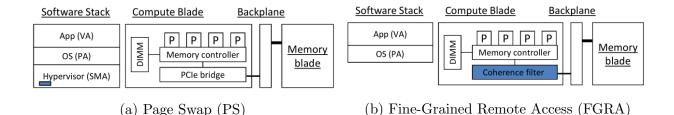

| 2.3 PS vs. FGRA remote memory system designs [25]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14       |

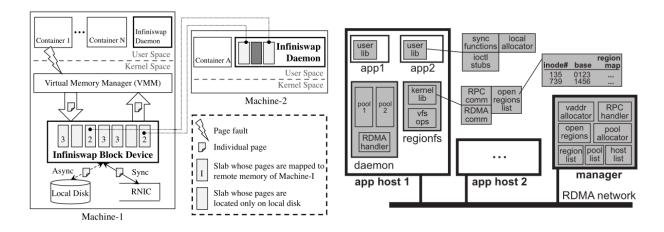

| 2.4 InfiniSwap Architecture [11]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16       |

| 2.5 Remote Regions Architecture [2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16       |

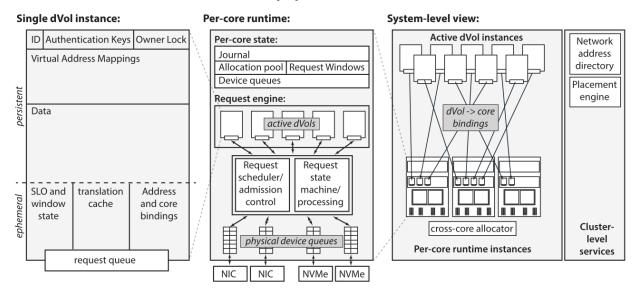

| 2.6 Decibel Architecture $[30]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16       |

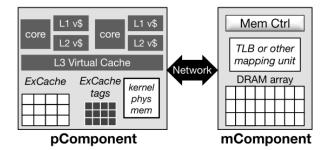

| 2.7 Lego OS pComponent and mComponent Architectures [36]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18       |

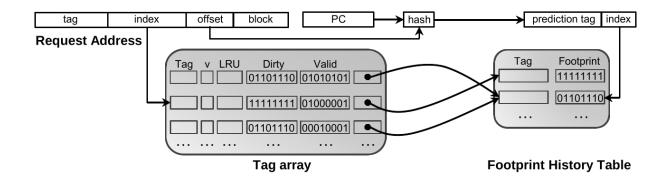

| 3.1 Footprint Cache tag array and footprint history table [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21       |

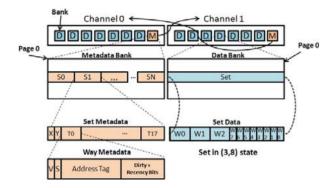

| 3.2 Bi-modal Cache data and tag layout [12]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

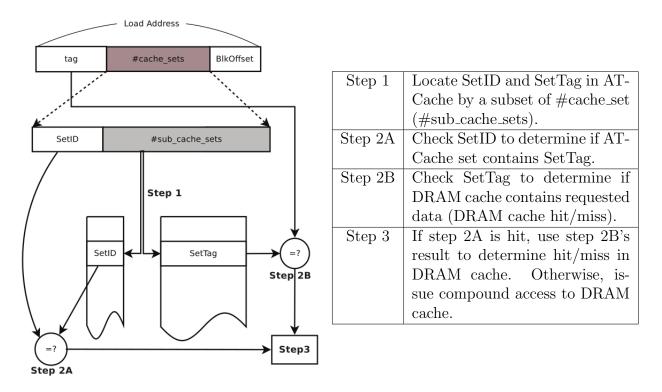

| 3.3 ATCache access logic $[37]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

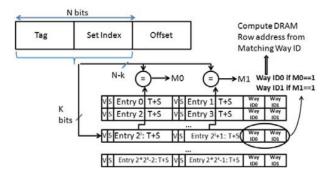

| 3.4 Way Locator [37]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

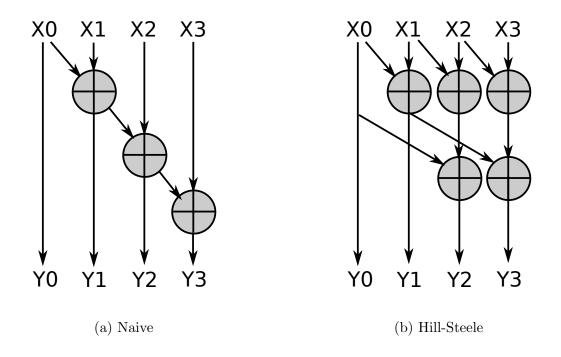

| 4.1 Prefix Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 4.1 Therefore the sum and the |          |

| 4.2 Chisel implementation of Yrenx Sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 4.4 Two different ways of implementing prefix sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 4.4 Two different ways of implementing prenx sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30<br>31 |

| 4.6 Prefix products using Scan generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 4.7 A Basic Rocket Chip SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

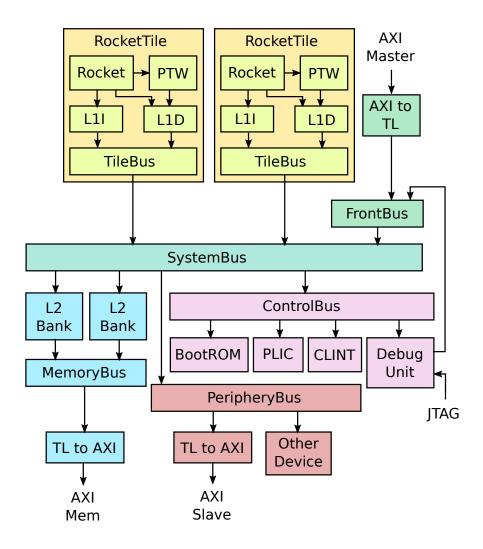

| 4.8 Big and Little Rocket Chip Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

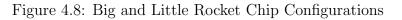

| 4.9         Hwacha [22]         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

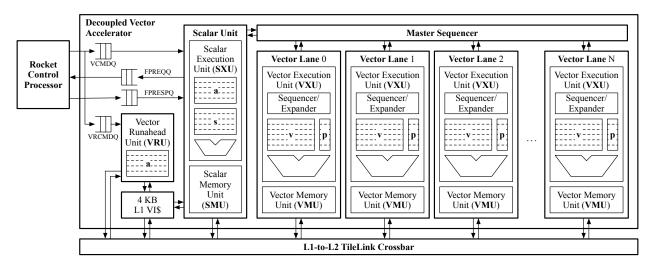

| 4.10 BOOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |

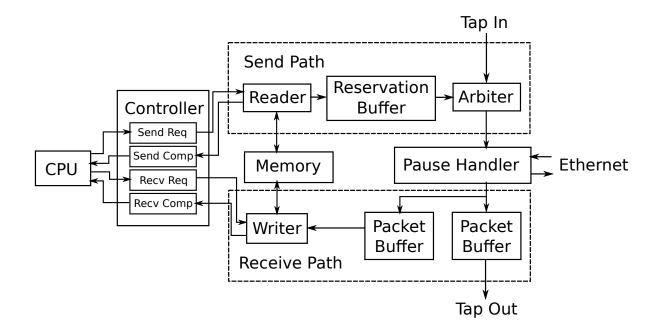

| 4.11 IceNet NIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

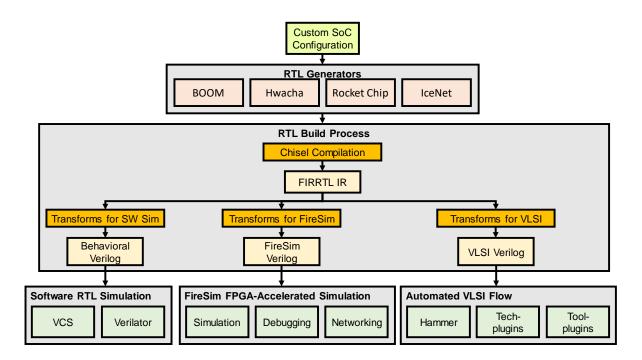

| 4.12 Complete Tool Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

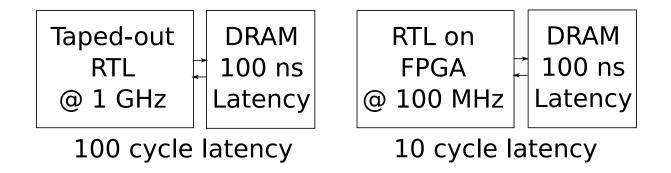

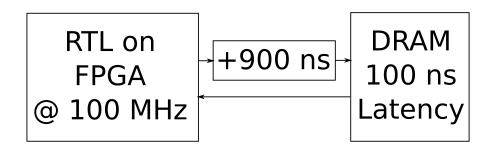

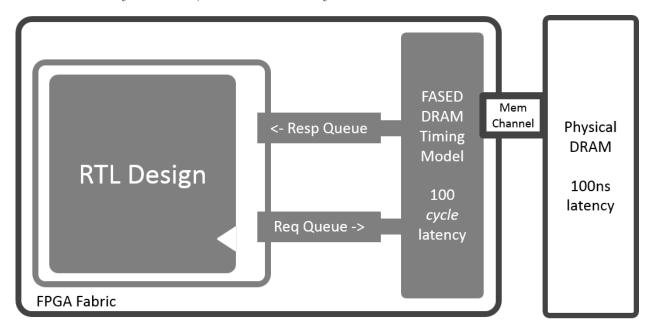

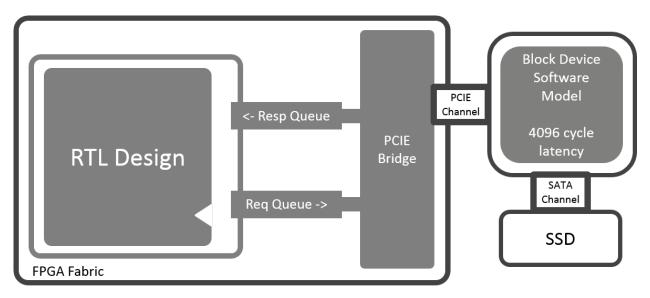

| $5.1 \\ 5.2 \\ 5.3$ | Comparison of Taped-out RTL (left) to its simulation on FPGA (right)40Latency Pipe Model40Golden Gate DRAM Model41                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.4                 | Golden Gate SSD Model    42                                                                                                                                                                |

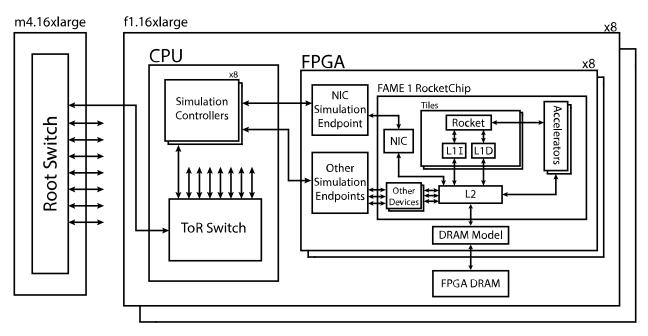

| 5.5                 | Mapping simulation to EC2 F1 in FireSim [18]                                                                                                                                               |

| 5.6                 | Example start and end trigger instructions                                                                                                                                                 |

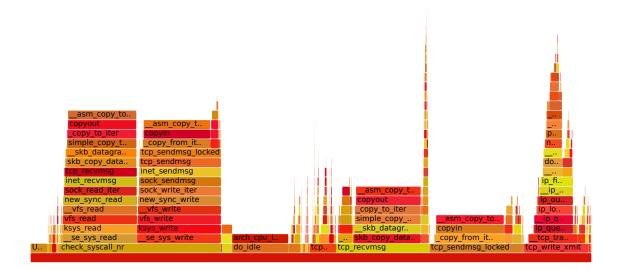

| 5.7                 | Example FirePerf Flame Graph [19]                                                                                                                                                          |

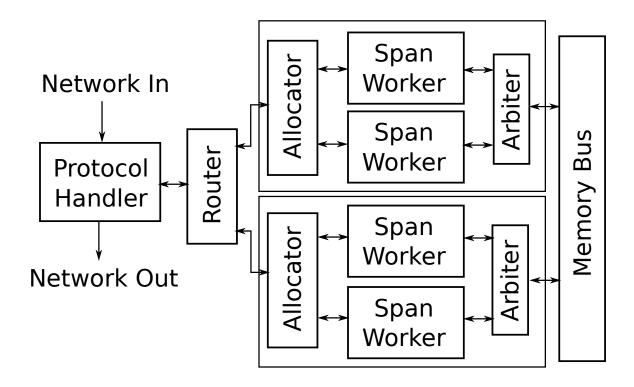

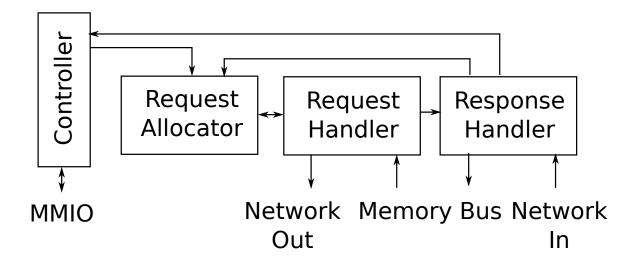

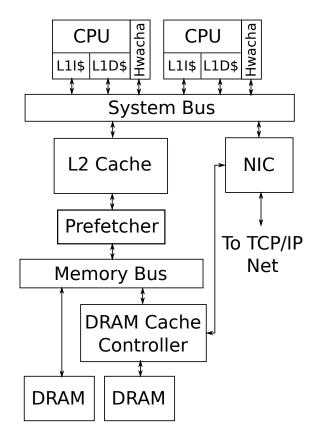

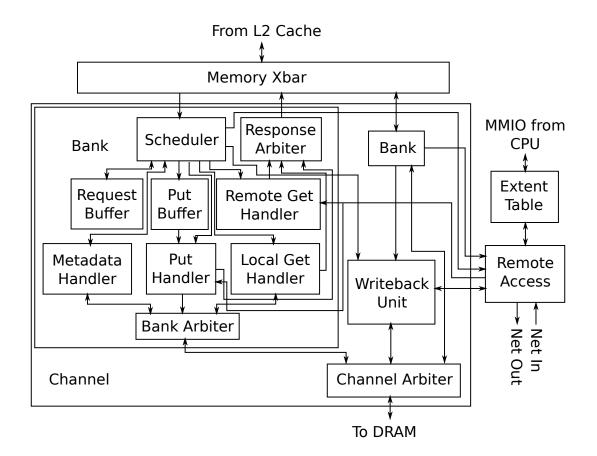

| $6.1 \\ 6.2$        | Memory Blade Design       50         Remote Memory Client Design       51                                                                                                                  |

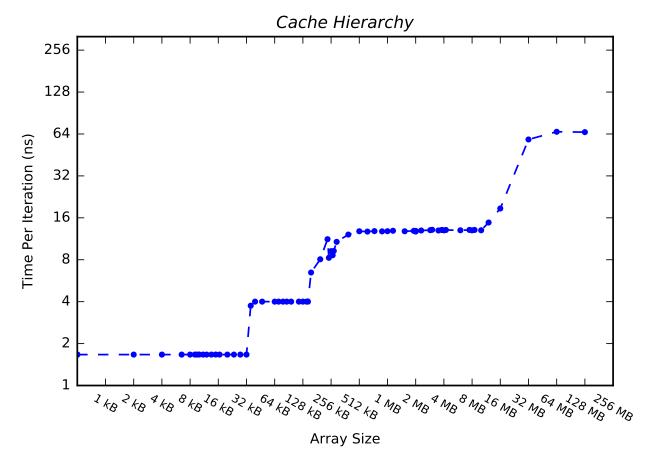

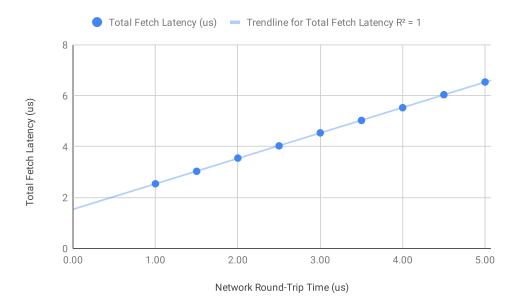

| 6.3                 | Firebox-0 CCBench results                                                                                                                                                                  |

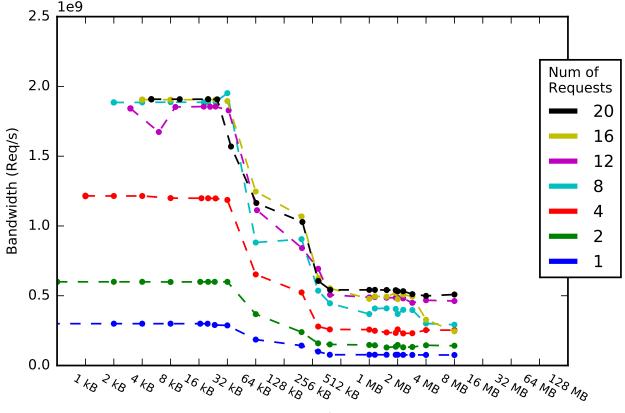

| 6.4                 | Firebox-0 band_req results                                                                                                                                                                 |

| 6.5                 | Latency of Remote Memory Access via Page Fault                                                                                                                                             |

| $7.1 \\ 7.2$        | DRAM Cache within SoC58DRAM Cache Design61                                                                                                                                                 |

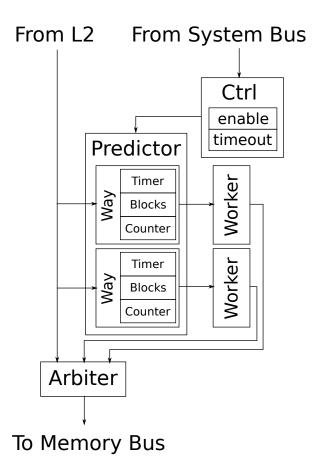

| 7.3                 | Prefetcher Design                                                                                                                                                                          |

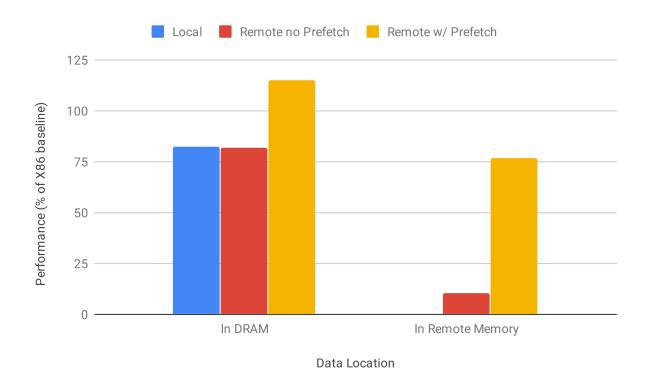

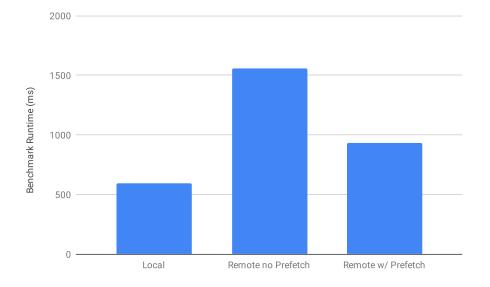

| 7.4                 | SAXPY Results                                                                                                                                                                              |

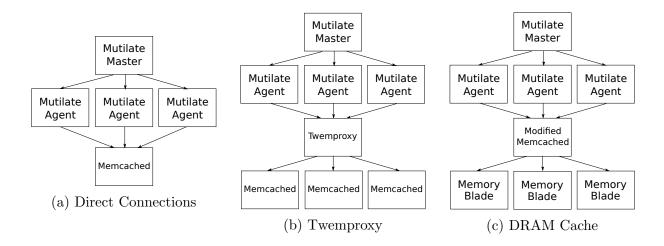

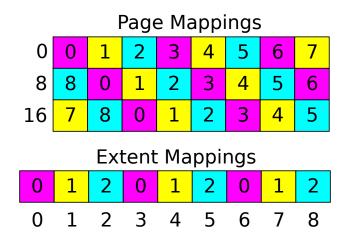

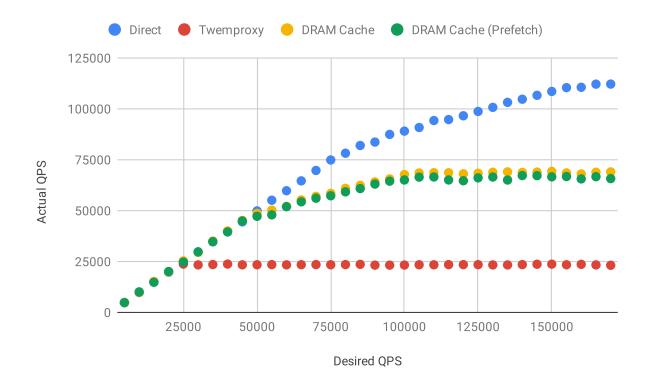

| 8.1<br>8.2<br>8.3   | Memcached Benchmark Configurations       70         Mapping of extents to memory blades (bottom) and pages to extents (top)       70         Mutilate Intended QPS vs. Actual QPS       72 |

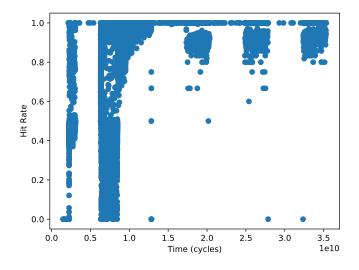

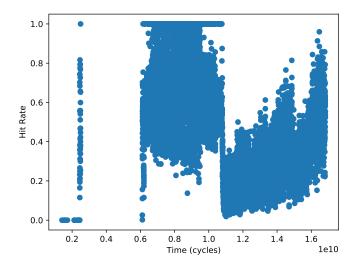

| 8.4                 | Hit Rate Over Time in Memcached Benchmark       73                                                                                                                                         |

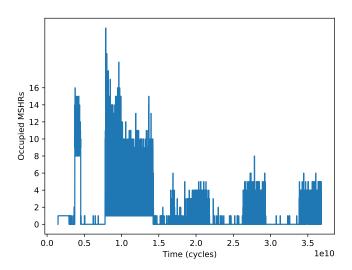

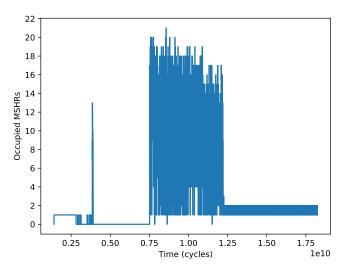

| 8.5                 | MSHR Occupancy Over Time in Memcached Benchmark                                                                                                                                            |

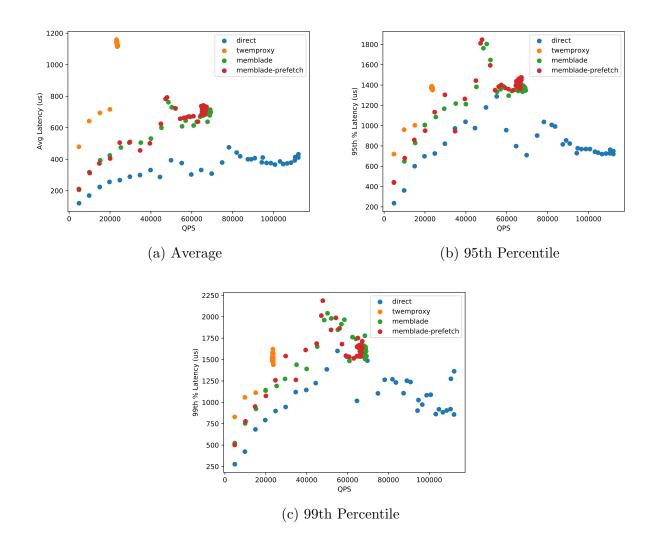

| 8.6                 | Mutilate QPS vs. Latency                                                                                                                                                                   |

| 8.7                 | Python reference implementation of friends-of-friends algorithm. The "graph"                                                                                                               |

|                     | argument is a dictionary mapping a vertex ID to a list of neighboring vertices.<br>The "user_id" argument is the ID of the user to find the friends-of-friends of 75                       |

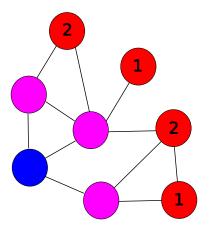

| 8.8                 | Sample friend graph showing the original user (blue), friends (magenta), and friends-of-friends (red). Numbers on FOFs indicate the number of mutual friends                               |

|                     | to original user                                                                                                                                                                           |

| 8.9                 | Friends-of-Friends Benchmark Results                                                                                                                                                       |

| 8.10                | Hit Rate Over Time in Friends-of-Friends Benchmark                                                                                                                                         |

| 8.11                | MSHR Occupancy Over Time in Friends-of-Friends Benchmark                                                                                                                                   |

# List of Tables

| 3.1 | Pros and Cons of Various DRAM Caching Techniques                  | 26 |

|-----|-------------------------------------------------------------------|----|

| 6.1 | Protocol request header                                           | 49 |

| 6.2 | Protocol response header                                          | 49 |

| 6.3 | Remote Memory Client Bandwidth and Latency Microbenchmark Results | 54 |

| 7.1 | DRAM Cache Parameters                                             | 63 |

| 7.2 | MemBench Results                                                  | 65 |

| 7.3 | Cache Hit Latency Breakdown                                       | 66 |

| 7.4 | Cache Miss Latency Breakdown                                      | 66 |

| 8.1 | Friends-of-Friends Benchmark Size Scaling                         | 78 |

#### Acknowledgments

This work would not be possible without the help and support of many people, including my professors, colleagues, and family.

I would first and foremost like to thank my adviser, Prof. Randy Katz, for his mentorship and guidance over the last several years. I also thank him for the financial support he has provided me in the last year of my PhD.

I would like to thank Prof. Krste Asanovic for financially supporting me over the majority of my PhD and for giving me his feedback as my second reader, and I would like to thank my third reader, Prof. Ian Holmes, for his feedback.

I would also like to thank my fellow graduate students in the ADEPT Lab. Together, we collaborated on the various tools that made this work possible. Alon Amid, David Biancolin, Adam Izraelevitz, Sagar Karandikar, Jack Koenig, Albert Magyar, Albert Ou, Nathan Pemberton, and Jerry Zhao, thank you all for your help and camaraderie. It has truly been a pleasure. Special thanks to Jerry for allowing me to use some of his block diagrams in Chapter 4.

And finally, I would like to thank my wonderful parents, Cungui Mao and Ruijuan Xu, for their love and support throughout my life. Thank you, Mom and Dad. I couldn't have gotten here without you.

# Chapter 1 Introduction

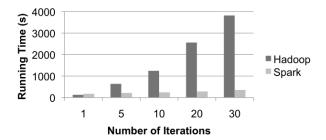

A major trend in data center workloads in the past decade has been increasing demand for memory. To deliver higher throughput or lower latency, application developers have increasingly been moving data that once resided in secondary storage into main memory. For instance, it has become common for web applications to cache the results of database queries in in-memory key-value stores like MemCached [9] or Redis [34]. This trend can also be seen in big data applications, where map-reduce frameworks which store intermediate results on disk, such as Hadoop, have been supplanted by frameworks which store intermediate results in memory, such as Apache Spark [42].

Figure 1.1: Comparison of Spark vs. Hadoop performance on Logistic Regression Benchmark [42]

## 1.1 The End of DRAM Cost/Density Scaling

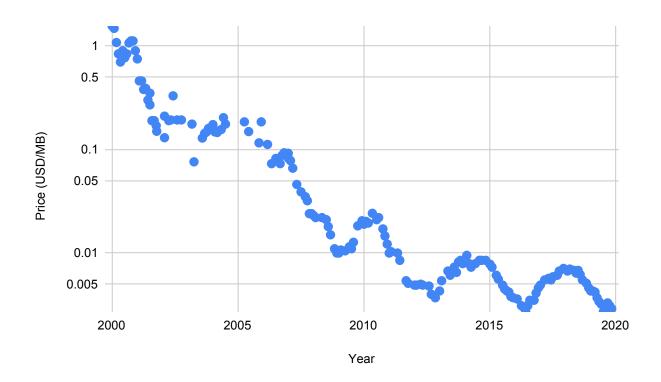

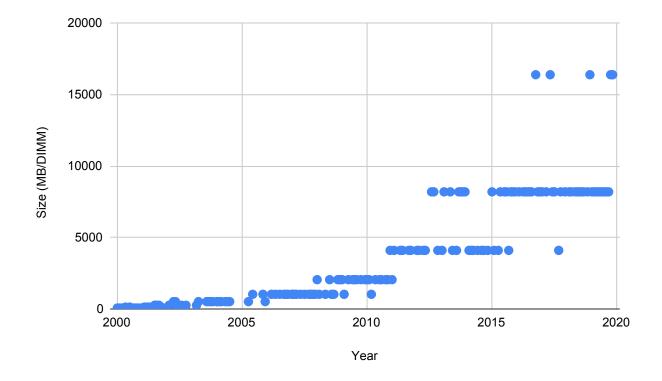

Advancements in memory technology have not kept pace with this increasing demand. Improvements in DRAM cost have plateaued in recent years, as shown in Figure 1.2 [29]. The same can be said for memory density, as the amount of memory that can fit on a single DIMM has been stagnant at around 8GB - 16GB for several years now (Fig. 1.3).

One promising avenue for further improvements is in new non-volatile random access memory (NVRAM) technologies, such as spin-transfer torque magnetic RAM (STT-MRAM), phase-change RAM (PCRAM), and resistive RAM (RRAM). These technologies promise to deliver storage density and persistence similar to that of solid-state drives, but with a much lower latency than conventional flash memory. As shown in Figure 1.4, all three types of NVRAM have similar read latency to DRAM. However, the latency of commercially-available NVRAM is still several orders of magnitude slower than DRAM. For instance, Intel's Optane NVRAM technology boasts a read latency of 7  $\mu s$  and write latency of 18  $\mu s$ . As high-end DDR4 memory can offer read latencies as low as 14 ns, it is clear that there is still a long way to go before NVRAM can function as a drop-in replacement for DRAM.

Figure 1.2: DRAM Cost over Time

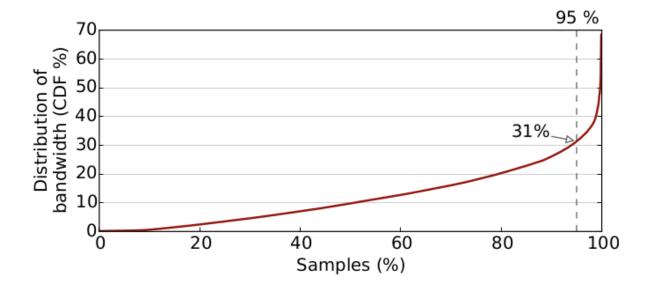

# **1.2** Poor Utilization of Memory in Data Centers